Feasibility Study of D3GaN Power Module for 2 Level 400V BEV Inverter

Dieter Liesabeths SVP of Products 28. March 2023

#### Agenda

- VisIC Company introduction

- Comparison of different GaN technologies to D<sup>3</sup>GaN

- Driver circuit

- Paralleling of D<sup>3</sup>GaN Devices

- Short circuit protection scheme

- Case Study 400V 2L BEV Inverter

- Outlook on next Power Modules

- Summary

### **Company Overview**

# **Company Overview**

- VisIC Technologies Ltd is a company established in 2010 under the laws of Israel

- Wholly owned subsidiary in Shanghai 微思芯电子技术(上海)有限公司, established in 2020

- Wholly owned subsidiary in Phoenix, AZ VisIC technologies LLC, customer support Packaging & Assembly, established in 2022

- Wholly owned subsidiary in Vienna, Austria, finalizing setup

- Agile supply chain as a fabless operation using

#### Locations

Visic Technologies HQ

VisIC Shanghai China Support

VisIC Reliability & Qualification

VisIC Munich Europe Sales

VisIC Hsinchu Operation

VisIC Sales APAC US

VP OPS

VisIC customer support,

VisIC Europe App Center

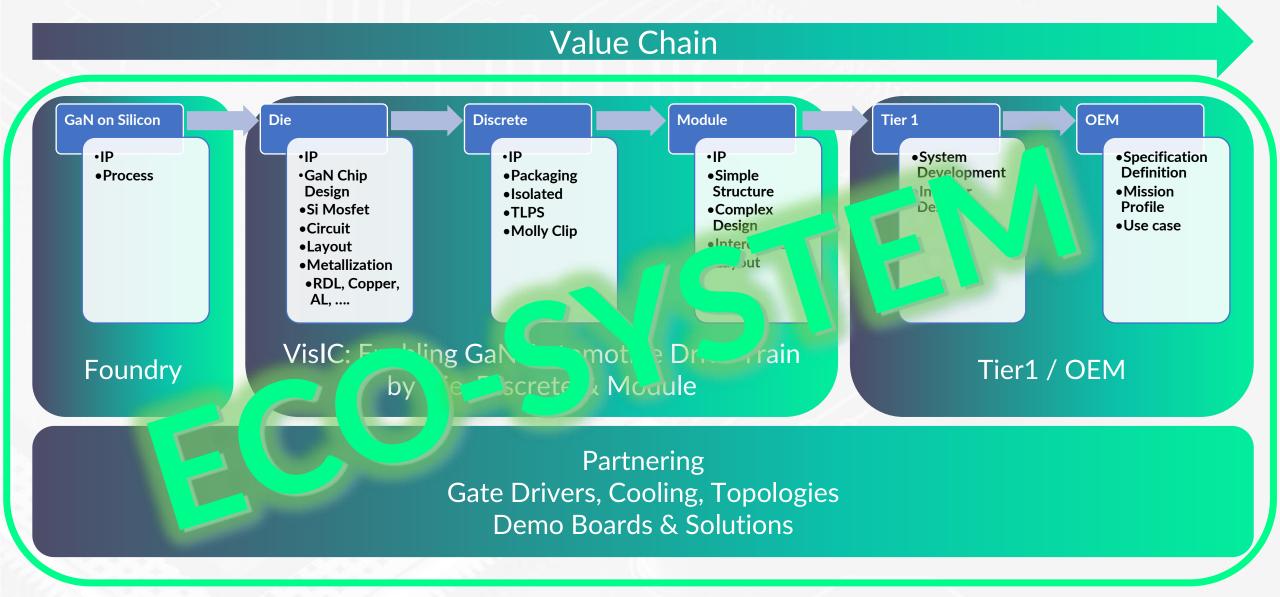

#### **VisIC Value Chain**

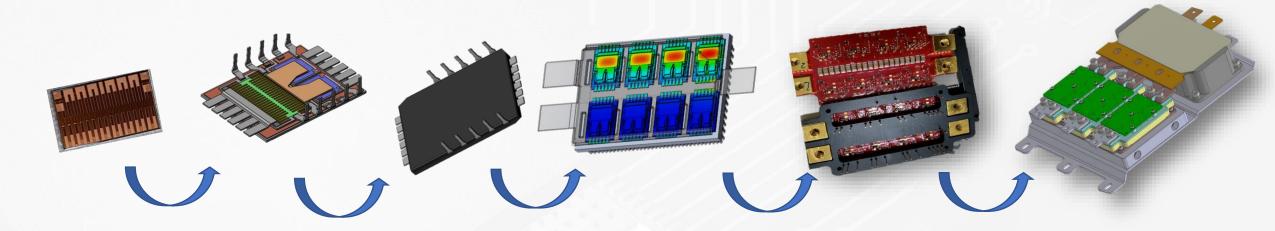

#### **Die to Inverter Integration**

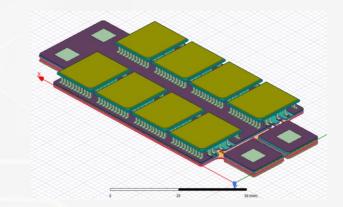

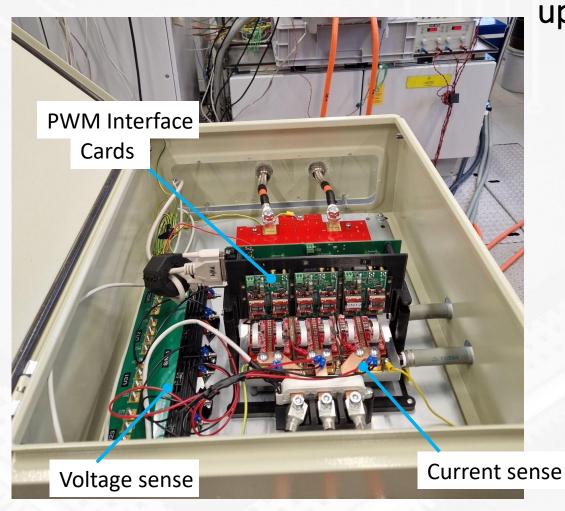

Technology vehicle: &00A HB module, open frame concept to speed up VisIC's and customer's learning curve

7 mOhm D-mode die > 200A current capability

Power board and control optimization process, high current (600A) testing,

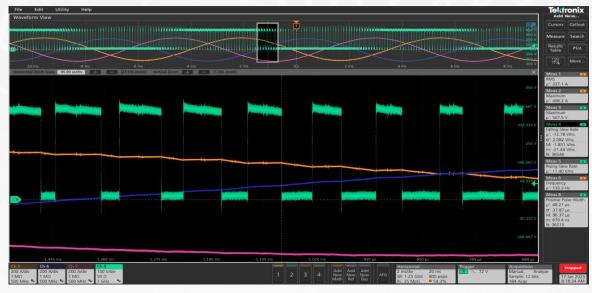

#### Fundamentals of Inverter Operation: Test data ACTUAL TEST DATA

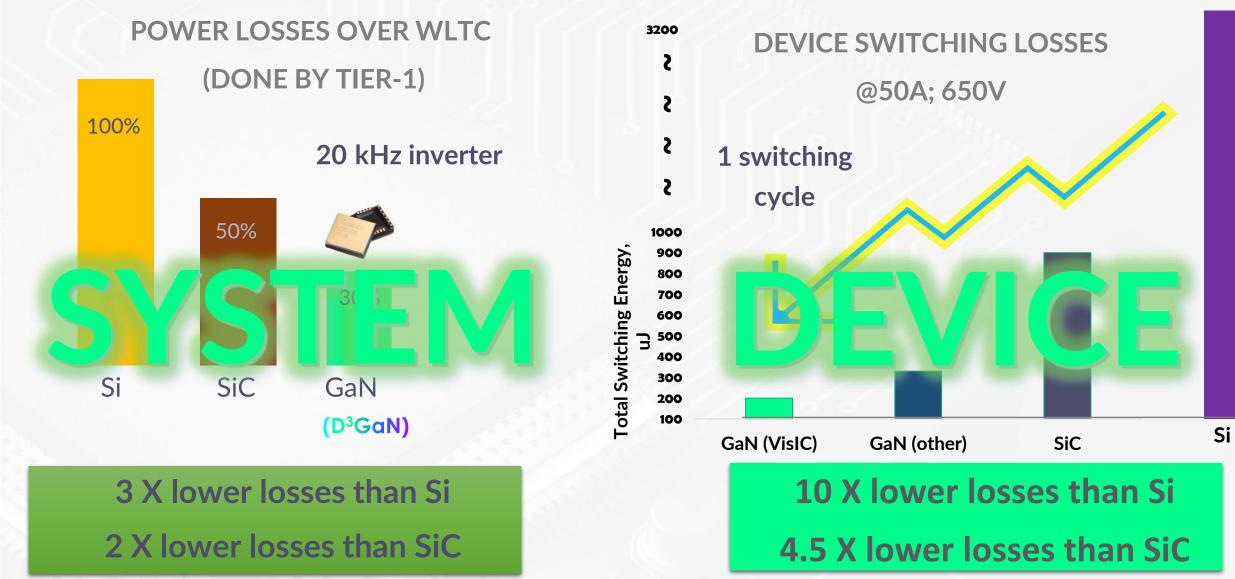

#### **Comparison of different GaN technologies**

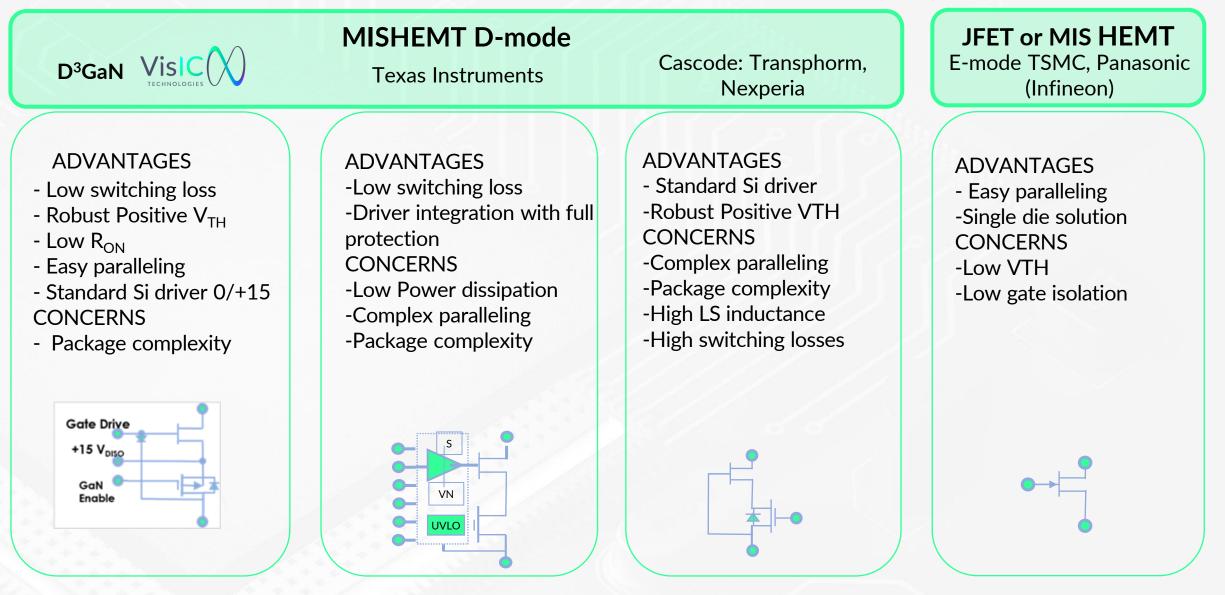

#### D<sup>3</sup>GaN vs Other GaN

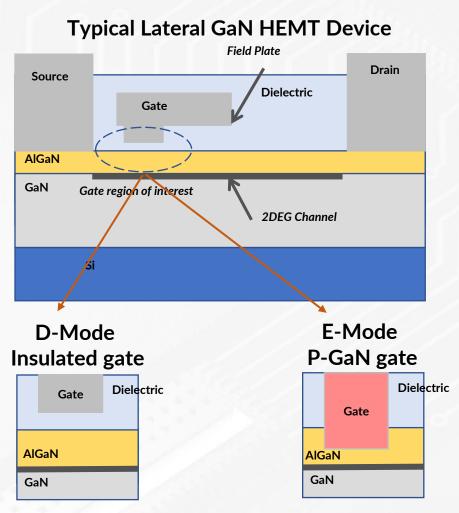

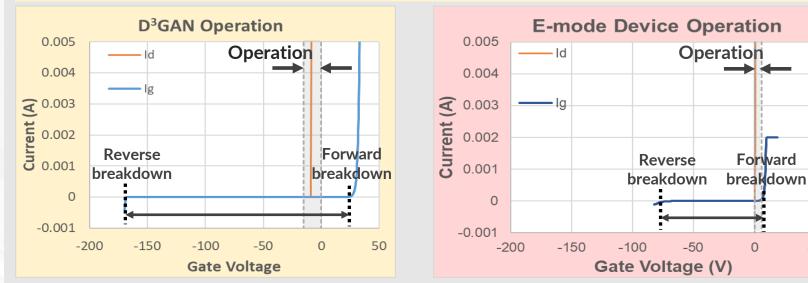

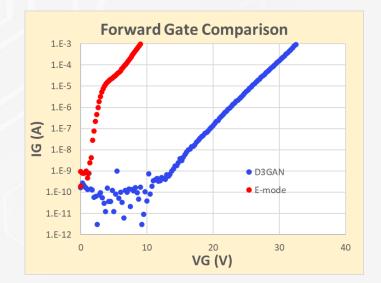

# D-mode vs E-mode GaN

- Depletion mode (d-mode)

- Normally on device

- Advantages

- Large negative threshold voltage

- Gate reliability not a concern

- Standard gate drivers can be used

- Disadvantages

- Must have circuitry to be normally off

- Uses cheap and reliable Si solutions

Enhancement Mode (e-mode)

- Normally off device

- Advantages

- Single chip solution

- Disadvantages

- Small margin to positive gate overvoltage

- Gate dielectric is critical

- Specialized gate drivers needed

- Sensitive to threshold voltage shift

D-mode provides easier path to product adoption in high reliability applications

### D-mode vs E-mode GaN

- D-mode is proven reliable technology widely employed in RADARs front end .

- D-mode has fundamentally lower specific RDSON for same class, due to absence of VT and RDRSON trade off

0

50

D-mode has fundamentally better reliability and robustness due to absence of doping-introduced . defects

### **Driver Circuit**

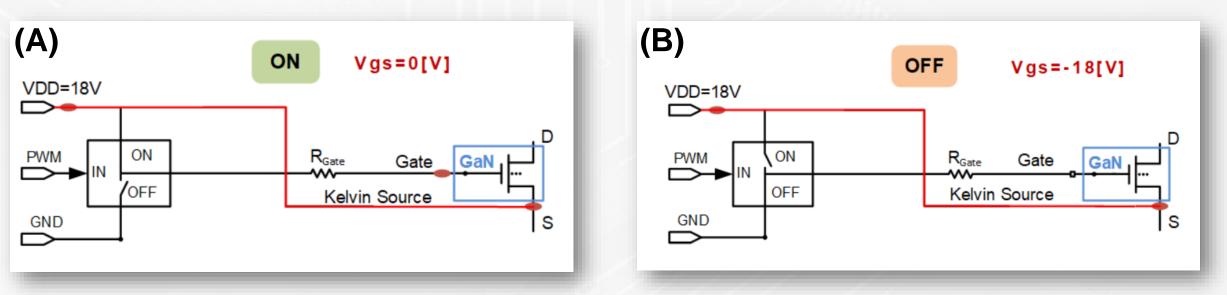

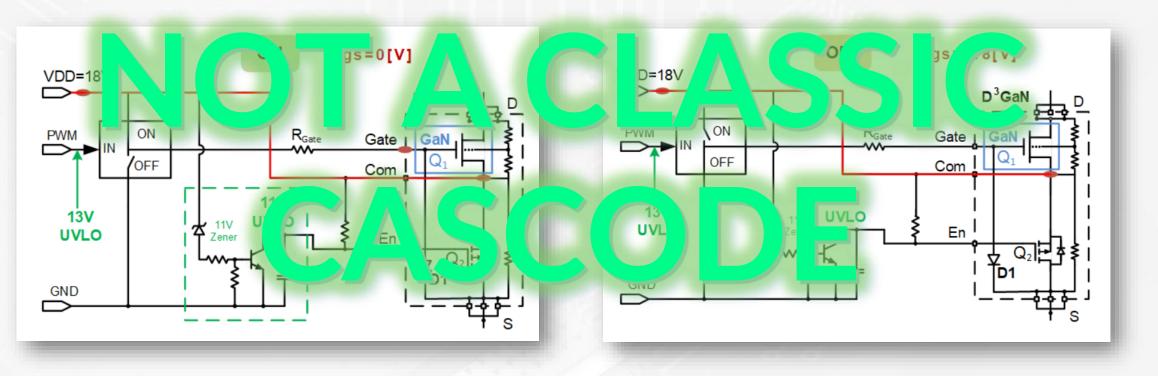

# D3GaN – Direct Drive D-Mode GaN (1of2)

Gate – Source potential difference [Vgs] equals the difference of driver output potential and driver (VDD) potential.

Threshold voltage of GaN is -8V, therefore when

- Gate to Kelvin potential is OV, GaN device is conducting (A)

- Gate to Kelvin potential is -18V, GaN device is not conducting (B)

Effective - Threshold Voltage is +10V

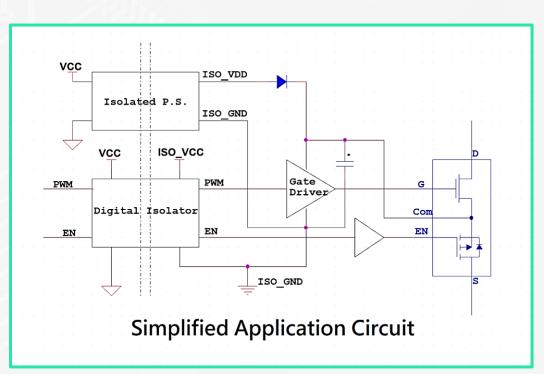

As SiC, D3GaN uses standard of-the-shelf gate drivers with a standard of-the-shelf Auxiliary Power Supply (VDD)

#### D3GaN - Direct Drive D-Mode GaN (2of2)

Q2 is ON when VDD is present and OFF when VDD is absent.

Q2 is not taking part in the switching process. It's held at "ON" during the switching of the D3GaN device

### Gate Drive D3GaN

#### **D3GaN Operation description**

- HV bias is applied to Drain-Source -> as Q2 is normally OFF, voltage rises on its Source. This induces negative Gate-Source potential on the GaN Gate, which is clamped to Drain of Q2 through Diode D1. When the negative GaN Gate-Source potential reaches the its threshold voltage of -8V it is turned off (in a similar fashion to a Cascode operation).

- HV bias is applied to Drain-Source and all control Pins are connected to the related pins of external driver IC, which is in power-off state without supplying of VDD. As Q3 in its OFF state the scheme operates as in case 1 preventing high current path to the driver.

- During normal device operation Q2 and Q3 are always in ON state -> GaN is driven directly from the driver and Q2 can be considered as a very small resistance.

#### **Paralleling of Devices**

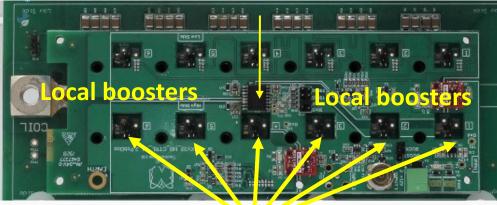

**Paralleling of multiple devices: driver consideration** Visic V Use one Master and few boosters

#### Master driver

Local boosters

Use a two matched power driver chips in one package driver, e.g. 2ED24427 that has two 10 Amp matched drivers

> Each driver drives two 8 mOhm GaN devices

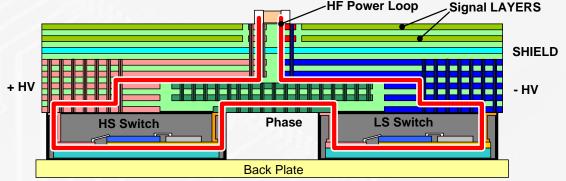

# Paralleling of multiple devices: layout design MAIN STEPS

- 1. Inductance reduction by minimizing the area enclosed by Power Loop

- 2. Increase current capability by adding layers and increasing Cu thickness

- Decrease of capacitive coupling between phase terminal and rest of the circuit:

by configuration of phase terminal

4. Reduction of HF noise coupling to control/driver circuits:

by partitioning of functional areas, shielding

|       | Trace cap<br>C[p |             | Stray Inductance<br>L[nH] |  |  |

|-------|------------------|-------------|---------------------------|--|--|

|       | +HV'-Phase       | -HV' -Phase | $\leq$                    |  |  |

| VM022 | 235              | 240         | 1.87                      |  |  |

#### Paralleling of multiple devices: device consideration/isIC( $\chi$ ) -0.999 High side Median = -7.8VAll switch 0.99 Sigma = 0.40

80% of the all

devices are good

the same module

to be assembled in

Verification of current sharing by direct measurement of voltage waveform on inductance of Q2

Low side

Measurement ground connection

Binning of devices by threshold voltage with "bin" size of +/- 0.5V

-12 -11 -10 -9 -8 -7 -6 -5

-1-1 #1000

N = 11063

measurement

points

0.05 0.02

0.005 -0.001

-1e-4

#### **Short Circuit Protection Scheme**

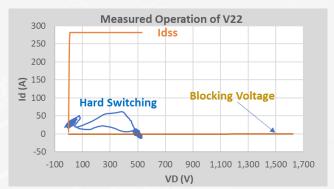

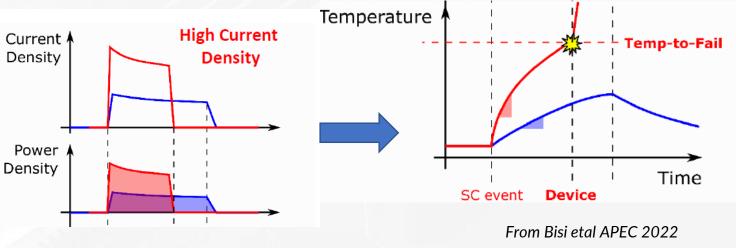

# **GaN HEMT Short Circuit Behavior**

- GaN devices have very high saturation currents

- 0.8 to 1.5 A/mm of gate periphery

- More than 1kA for D<sup>3</sup>GAN devices

- Power density rises rapidly with increasing current and exceeds the thermal capability of the device even at low voltages

- Saturation current does not reached

- Failure will occur in ~0.3 μsec

- Typical protection schemes rely on 1 to 2 µsec to respond to rising current

Lateral GaN devices require different approach to surge current protection

© VisIC Technologies 2023 - Public

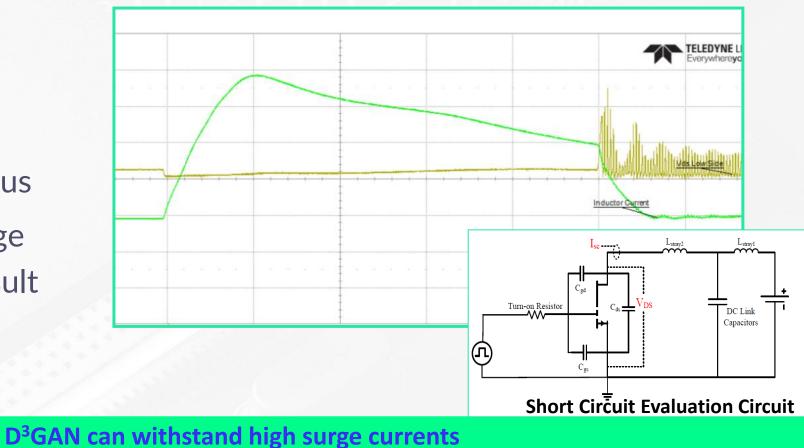

# **Initial Surge Current Capability Evaluation**

- GaN devices do not operate in at or near the saturation region

- No internal limitation to device current during a short circuit event

- Proper current limiters are needed for safe operations

- **!** See App note

- Preliminary results for

80A rated device show

operation of 395A for 5us

- Failures in standard surge current testing were result of voltage spike during turn off

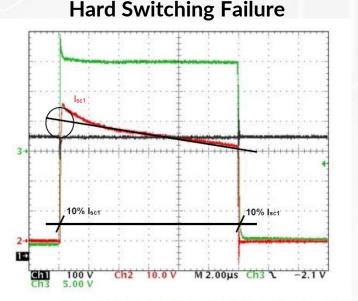

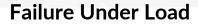

# **Short Circuit Testing From AQG 324**

#### • Two types of tests defined in AQG 324

Figure 7.7: Typical short circuit type 1 behavior of an IGBT Ch1:  $V_{CE}$  (100 V/Div), Ch2: IC (10 A/Div), Ch3:  $V_{GE}$  (5 V/Div)

• Both tests reference the saturation current (not applicable in lateral GaN)

- Hard switching failure testing uses limited inductances to prevent reaching saturation

- Failure under load must not desaturate within 5 usec

**Current guidelines do not address the unique nature of lateral GaN**

# **Surge Current Protection**

- Commercial short circuit protection schemes do not protect GaN power devices

- Device heats up and fails @ 0.3 usec versus the 1 – 2 μsec of circuit response time

- Circuits typically use saturation voltage sense to trigger

- Developed circuit that will sense and turn off device more quickly

- Soft turn-off (1st stage) in < 0.3usec

- Final turn-off (2nd stage) in 0.5 usec

- Derivative circuit that triggers on rate of change and on current level

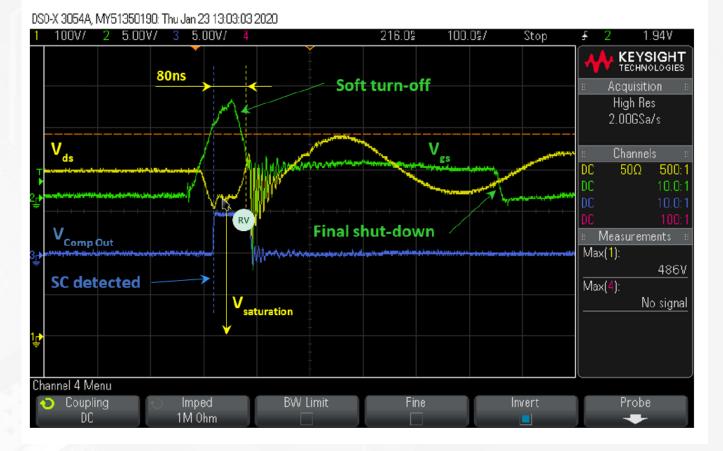

#### SC Protection Application Note APN-01650-0003 Rev1.0

Yellow - Vds 100 V/div Green - Vgate 5 V/div Blue - comparator output 5V/div Red - Coil current Horizontal: 200 ns/div

#### 2 stage turn off provides better protection

#### © VisIC Technologies 2023 - Public

#### **Over Current Protection**

- Short circuit event has small drop in VD in GaN

- SC protection circuit senses the rapid change in current

- Comparator circuit on Q2 (Silicon LV FET)

- Starts shutdown procedure within 80nsec

- Stage 2 shutdown within ~ 500 nsec

**Over current protection begins in 80ns**

### **SC Protection Circuit on Parallel Devices**

- Parallel operation of devices allows device failures to influence all devices

- Demonstrated protection of SC on a single device does not necessarily correlate with devices in parallel

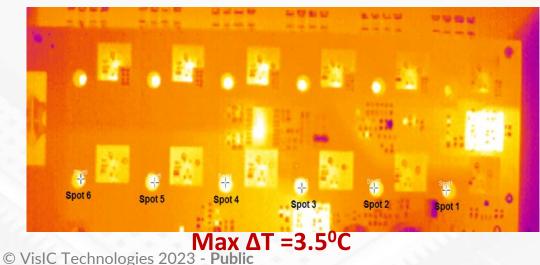

- VisIC SC protection method has been applied to a 6 pack board (12 devices in parallel )

- Half bridge configuration

|        | vice Surge Cu | ırrent Testing   | Copper foil to<br>simulate short<br>circuit |         |   |  |

|--------|---------------|------------------|---------------------------------------------|---------|---|--|

| Coil   | Vin           | Response<br>time |                                             |         |   |  |

| 3.2µH  | 400V          | <500ns           |                                             |         |   |  |

| 0.55μΗ | 400V          | ~200ns           |                                             | <u></u> | • |  |

| 2nH    | 300V          | ~100ns           |                                             |         |   |  |

| 2nH    | 400V          | ~100ns           |                                             |         |   |  |

• All conditions resulted in a controlled shutdown and no damage to any additional die

SC protection of D<sup>3</sup>GAN has been demonstrated on parallel device

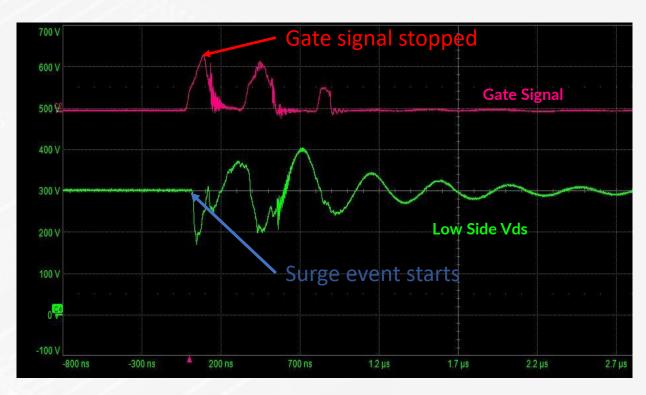

# **Surge Current Results for Parallel Devices**

- Copper foil jumper used to simulate short circuit

- 2nH inductance

- Input voltage = 300V

- Initiation of the shutdown procedure is ~ 100ns after surge even occurs

- Board verified to be fully functional after testing

#### Full protection of board has been demonstrated

#### Case Study 400V 2L BEV Inverter

#### **Tested at OEM with motor**

© VisIC Technologies 2023 - Public

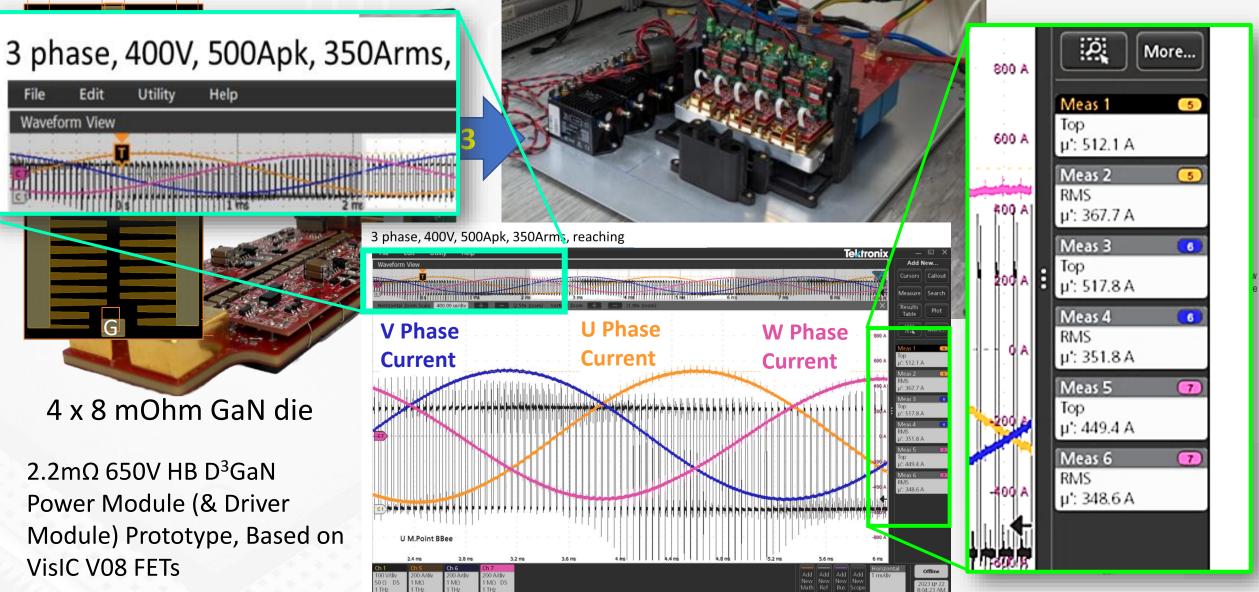

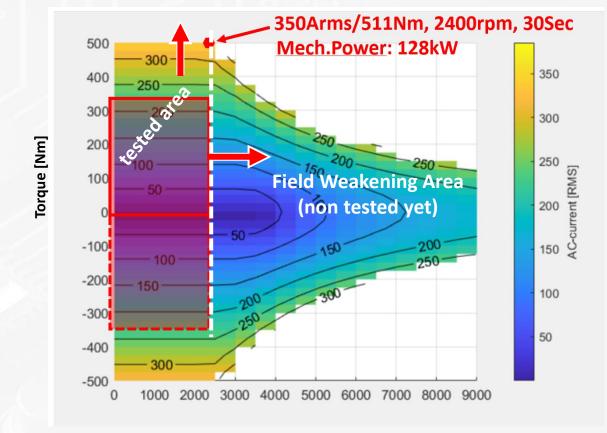

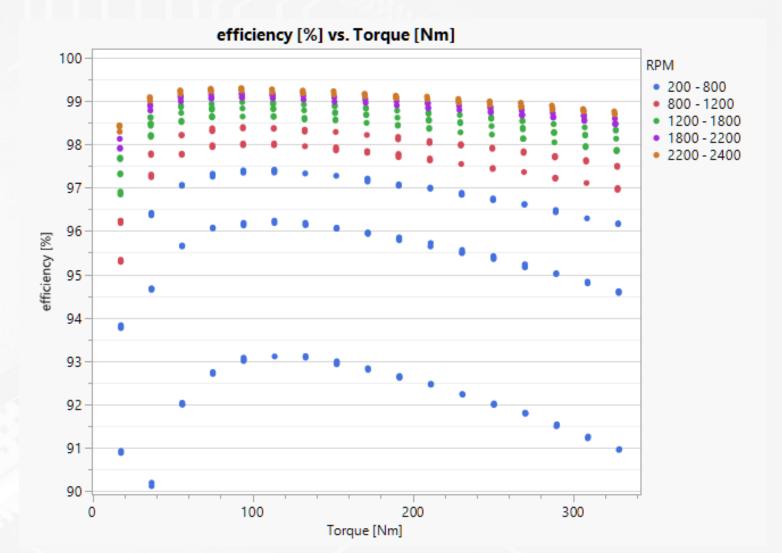

#### Results: 400V EV GaN based prototype

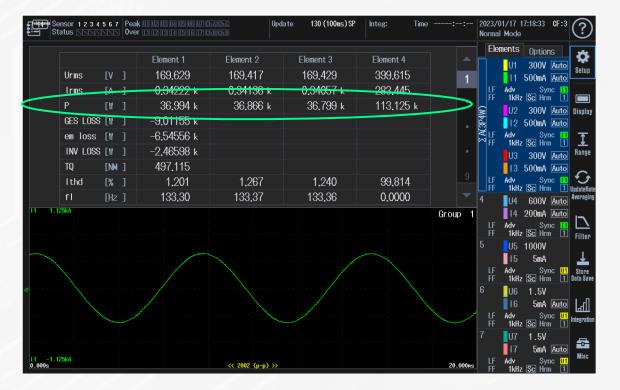

3-Phase GaN Inverter , Closed loop DYNO set up, tested up to 113 kW

Speed [rpm]

© VisIC Technologies 2023 - Public

### High Power Operation Achieved 350Arms (500A peak) @400V for 30sec

| Se St                                 | ensor 1234<br>atus NNN | 567 |      | U3 U4 U5 U6 U7 (<br>13 14 15 16 17 ( |              | Update | 130 (100ms) SP | Integ:    | Time::   |

|---------------------------------------|------------------------|-----|------|--------------------------------------|--------------|--------|----------------|-----------|----------|

|                                       |                        |     | Ele  | ement 1                              | Element 2    |        | Element 3      | Element 4 |          |

|                                       | Urms                   | [V  | ] 1  | 69.629                               | 169.417      |        | 169.429        | 399.615   | 5 1      |

|                                       | lrms                   | [A  | ] 0  | .34222 k                             | 0.34136      | k      | 0.34057 k      | 283.445   |          |

|                                       | Р                      | EW  | ]    | 36.994 k                             | 36.866       | k      | 36.799 k       | 113.125   | ò k 👘    |

|                                       | GES LOSS               | EW  | ] –9 | .01155 k                             |              |        |                |           |          |

|                                       | em loss                | EW  | ] –6 | .54556 k                             |              |        |                |           |          |

|                                       | INV LOSS               | EW  | ] –2 | .46598 k                             |              |        |                |           |          |

|                                       | TQ                     | ENM | ] 4  | 97.115                               |              |        |                |           |          |

|                                       | lthd                   | [%  | ]    | 1.201                                | 1.267        |        | 1.240          | 99.814    | 9        |

|                                       | fl                     | [Hz | ]    | 133,30                               | 133.37       |        | 133.36         | 0.0000    | ) –      |

| · · · · · · · · · · · · · · · · · · · | 25kA                   |     |      |                                      |              |        |                |           | Group 1  |

| <br>11 -1.1<br>0.000s                 | 25kA                   |     |      |                                      | << 2002 (p-p | ) »>   |                |           | 20.000ms |

|                                       |                        |     |      |                                      |              |        | 24             | 00 RPI    | Л        |

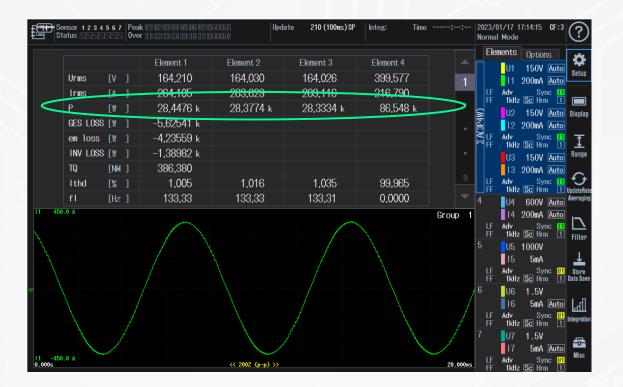

### **High Efficiency**

400V 280ARMS 2000RPM 30sec -Efficiency 98.39% @10V/ns

400V 350ARMS 2000RPM 30sec -Efficiency 97.82% @10V/ns

#### WLTP Driving Cycle Efficiency

> 99.295%

> 2400RPM (160Hz)

> 92.8NM

> 24.4KW output

□ Max Efficiency point:

# **Future Outlook**

#### VisIC GaN Module Outlook

#### VM022 Prototype based on 4x parallel discrete V08 SMD

# 4.4mΩ 650V Half-Bridge D³GaN™ Power Module

#### Description

The Transfer Molded Half Bridge module integrates 8mΩ Power FETs for a 300A<sub>me</sub> class inverter and can be paralleled for higher power. The D<sup>3</sup>GaN<sup>™</sup> technology uses high-density. lateral GaN power transistor, assembled into a Normally-Off product with extremely low RDS(ON) and exceptionally efficient switching performance.

The integrated safety functions ensure safe operation during system start up and shutdown, while having no impact on the switching performance of the GaN transistor.

#### **Key Features**

- Low inductance terminal connection to Busbars

- Weldable power terminals

- Thermal case designed for sintering to the heatsink

- · High Threshold voltage for fast switching transients

- High performance SiN ceramic substrate

- Standard 15V gate drive voltage

- NTC sensor

- Package Size 50x38x6mm

#### Applications

- Hybrid and Electric Vehicle Traction Inverter

- High Power DC-DC Converter

#### **Key Performance Parameters**

| Parameter                 | Value |

|---------------------------|-------|

| V <sub>DS</sub> (V)       | 650   |

| R <sub>Ds</sub> (on) (mΩ) | 4.4   |

| Q₀(nC)                    | 222   |

| l⊳(A)                     | 360   |

|                          | VM044     |

|--------------------------|-----------|

| Power Loop               | 5.7nH     |

| Miller Current Gate Loop | 3nH       |

| Size                     | 50x38x6mm |

#### VM044 2x V08/switch position Sample Available Q3 2023

# Summary

### **Summary**

#### Today

- ✤ D<sup>3</sup>GaN reliable operation for high current BEV Inverter application

- Proof of paralleling & short circuit detection methodology

#### Future Works

- Higher integration of Power Modules using 2nd Gen D3GaN chip for scalable inverter solutions

- ✤ 3 Level NPC Inverter topologies to serve 800V BEV battery market

# **THANK YOU**